Zuverlässigkeitsprüfung von Leiterplatten bei hohen und niedrigen Temperaturen: Überprüfung der Lebensdauer der Leiterplatte unter thermischer Belastung

2026-04-03 16:25Die Temperatur ist der wichtigste Umweltfaktor, der die Zuverlässigkeit von Leiterplatten beeinflusst. Von extremer Kälte im Freien bei minus zehn Grad Celsius bis hin zu hohen Temperaturen im Inneren von Geräten bei mehreren hundert Grad Celsius ist die Leiterplatte ständig thermischer Ausdehnung und Kontraktion ausgesetzt. Zuverlässigkeitsprüfungen bei hohen und niedrigen Temperaturen bewerten die strukturelle Stabilität und die elektrische Leistungsfähigkeit von Leiterplatten unter thermischer Belastung durch die Simulation extremer Temperaturänderungen. Sie sind ein zentraler Prüfpunkt für hochzuverlässige Leiterplatten in der Automobilelektronik, der Rüstungsindustrie und der industriellen Steuerungstechnik.

Leiterplatten bestehen aus Epoxid-/Polyimid-Substraten, Kupferfolien, Lötmitteln, Keramikbauteilen und anderen heterogenen Materialien. Der Wärmeausdehnungskoeffizient (CTE) dieser Materialien variiert stark: Kupfer hat einen CTE von ca. 17 ppm/°C, das Epoxidharz-Substrat von 13–50 ppm/°C, das Lötmittel von ca. 25 ppm/°C und die Keramikbauteile von nur 6–8 ppm/°C. Bei Änderungen der Umgebungstemperatur dehnen sich die Materialien unterschiedlich stark aus oder ziehen sich zusammen, wodurch an den Grenzflächen Scher- und Zugspannungen entstehen. Kurzfristige Temperaturänderungen verursachen geringere Spannungen und führen nicht zu offensichtlichen Ausfällen. Langfristige, wiederholte Temperaturwechsel hingegen führen zu einer kontinuierlichen Spannungsakkumulation und schließlich zu Materialermüdung der Leiterplatte. Dies ist das Kernprinzip von Hoch- und Tieftemperaturtests. beschleunigte thermische ErmüdungsalterungDie

Die Prüfung von Leiterplatten bei hohen und niedrigen Temperaturen lässt sich im Wesentlichen in zwei Kategorien unterteilen: Temperaturwechselprüfung Und Kälte- und HitzeschockprüfungEs bestehen deutliche Unterschiede in der Belastbarkeit und den Anwendungsbereichen. Der Temperaturwechseltest ist die gängigste Methode zur Überprüfung der Hoch- und Tieftemperaturbeständigkeit. Die Testanlage ist eine Wechseltemperaturkammer, in der die Temperatur programmgesteuert langsam zwischen den Bereichen wechselt. Die Temperaturanstiegs- und -abfallrate beträgt üblicherweise 1–5 °C/min, die Verweildauer in einer Temperaturzone 15–30 Minuten. Dadurch werden die leichten Temperaturschwankungen simuliert, die durch das Starten und Stoppen von Geräten sowie durch den Wechsel der Jahreszeiten entstehen. Der übliche Temperaturbereich in der Industrie liegt zwischen -40 °C und 125 °C, die Anzahl der Zyklen zwischen 500 und 1000. Bei Unterhaltungselektronik kann der Bereich auf -20 °C bis 85 °C vereinfacht werden, während Automobilelektronik die strengen Anforderungen von -55 °C bis 150 °C erfüllen muss.

Die Temperaturwechselprüfung ist ein Verfahren zur Überprüfung der thermischen Beanspruchung. Dabei wird die Leiterplatte in einer Zwei- oder Dreikammer-Schockkammer innerhalb von weniger als einer Minute extremen Temperaturwechseln zwischen 125 °C und -55 °C ausgesetzt. So werden unmittelbar enorme thermomechanische Belastungen erzeugt und potenzielle Defekte in der Leiterplatte schnell sichtbar gemacht. Dieses Verfahren wird hauptsächlich unter extremen Betriebsbedingungen eingesetzt, beispielsweise bei Leiterplatten für den Militärbereich, die Luft- und Raumfahrt sowie für Motorräume in der Automobilindustrie. Es ermöglicht die schnelle Aussortierung von Produkten mit unzureichender thermischer Stabilität. Der Testzyklus ist deutlich kürzer als bei der Temperaturwechselprüfung, die Belastung der Leiterplatte ist jedoch erheblich.

Das branchenübliche System für Hoch- und Tieftemperaturprüfungen ist umfassend und beinhaltet unter anderem IPC-TM-650 2.6.7 (Temperaturwechselprüfung für Leiterplatten), JEDEC JESD22-A104 (Temperaturwechselprüfung für Halbleiter und Leiterplatten) und IEC 60068-2-14 (Temperaturwechselprüfung). Zu den nationalen Normen zählen GB/T 2423.22 (Wechselprüfung zwischen hohen und niedrigen Temperaturen) und GJB 150.3A (Hoch-/Tieftemperaturprüfung für militärische Ausrüstung). Die spezielle Norm für Automobilelektronik ist AEC-Q104. Sie legt die Hoch- und Tieftemperaturprüfparameter sowie die Ausfallkriterien für Automobil-Leiterplatten fest und stellt die Zulassungsvoraussetzung für Leiterplatten in Fahrzeugen mit alternativen Antrieben dar.

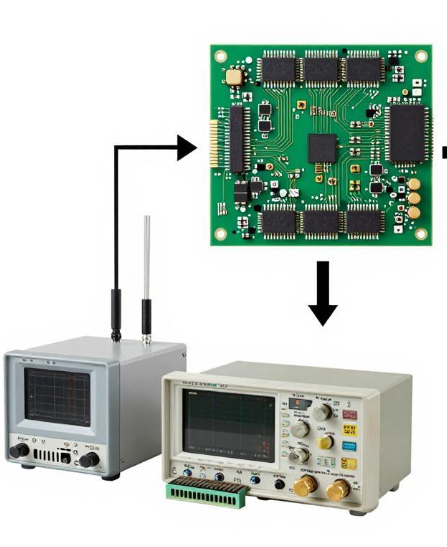

Der Testprozess folgt strikt den standardisierten Schritten: Zunächst wird die Probe vorgetestet. Dabei werden der anfängliche Durchlasswiderstand, der Isolationswiderstand und die Impedanz der Leiterplatte mit einem Multimeter und einem LCR-Tester erfasst. Durch Sichtprüfung und Röntgenprüfung wird sichergestellt, dass keine anfänglichen Lötstellenrisse oder Substratdefekte vorliegen. Anschließend wird die Leiterplatte in der Testkammer fixiert, um ein Verrutschen während des Tests zu verhindern. Temperaturbereich, Temperaturanstiegs- und -abfallrate sowie die Anzahl der Zyklen werden gemäß Standard eingestellt. Während des Tests können die Änderungen der elektrischen Eigenschaften in Echtzeit über die Online-Überwachungseinrichtung aufgezeichnet werden. Nach Abschluss des Tests erfolgt eine umfassende Prüfung, die eine Sichtprüfung (Lötstopplackblasen, Substratablösung, Bauteilrisse), eine Röntgenprüfung (BGA-Lötstellen, interne Risse in Durchkontaktierungen) und eine Prüfung der elektrischen Eigenschaften (Widerstandsänderungsrate ≤ 5 %, Isolationswiderstand ≥ 100 MΩ) umfasst.

Die typischen Ausfallarten von Leiterplatten in Umgebungen mit hohen und niedrigen Temperaturen lassen sich hauptsächlich in drei Kategorien einteilen: Lötstellen, Durchgangslöcher und SubstrateUnter thermischer Belastung neigt die Grenzfläche zwischen Lötpad und Lötmittel zu Mikrorissen. Mit zunehmender Zyklenzahl breiten sich diese Risse aus und führen schließlich zum Bruch der Lötstelle. Dies betrifft insbesondere Lötstellen von Gehäusebauteilen wie BGA und QFN, die aufgrund von Spannungskonzentrationen anfälliger für Ausfälle sind. Der Ausfall von Durchkontaktierungen in mehrlagigen Leiterplatten hängt mit verschiedenen inneren Lagen zusammen. Die durch thermische Ausdehnung und Kontraktion erzeugte axiale Spannung zieht an der Kupferbohrung, was zu Rissen in der Kupferschicht und Leiterbahnbrüchen führt. Substratfehler umfassen Harzablösung, Glasfaserbruch und Ablösung der Lötstoppmaske, hauptsächlich aufgrund ungeeigneter Substratauswahl oder Fehlern im Pressvorgang.

Um das Ausfallproblem bei hohen und niedrigen Temperaturen zu beheben, kann die Zuverlässigkeit durch Optimierung in drei Bereichen verbessert werden: Design, Material und Prozess. Bei der Materialauswahl werden für hochzuverlässige Leiterplatten Hochfrequenz- und Hochgeschwindigkeitssubstrate mit niedrigem Wärmeausdehnungskoeffizienten (z. B. Rogers- und Shengyi-Hochfrequenzmaterialien) verwendet, um Unterschiede in der Wärmeausdehnung zu minimieren. Die Lötstellen bestehen aus einer Lötlegierung mit höherer Zähigkeit, und das Pad-Design ist optimiert, um die Spannungsfläche der Lötstelle zu vergrößern. Im Hinblick auf das Strukturdesign wird vermieden, große Bauteile in Bereichen mit hoher Spannungskonzentration auf der Leiterplatte zu platzieren. Versteifungen oder Befestigungslöcher werden hinzugefügt, um die Amplitude der thermischen Verformung zu reduzieren. Die Durchkontaktierungen sind mit verdicktem Kupfer und Sacklöchern versehen, um die Zugfestigkeit zu verbessern. In Bezug auf die Prozesstechnologie werden die Presstemperatur und der Pressdruck streng kontrolliert, um die Haftkraft zwischen den Substratschichten zu gewährleisten. Die Temperaturkurve des Reflow-Lötens wird optimiert, um die Restspannung in der Lötstelle zu reduzieren.

Mit der zunehmenden Integration hochdichter Leiterplatten verschärfen sich die Herausforderungen hinsichtlich der Zuverlässigkeit von 3D-MID-, Rigid-Flex- und ultradünnen Leiterplatten bei hohen und niedrigen Temperaturen. Der Wärmeausdehnungskoeffizient (CTE) der starren und flexiblen Bereiche starrer und starrer Verbundplatten unterscheidet sich stark, wodurch es unter Temperaturwechselbeanspruchung leicht zu Verbindungsbrüchen kommen kann. Die Substratsteifigkeit ultradünner Leiterplatten ist unzureichend, sodass sie sich bei hohen Temperaturen leicht verziehen und verformen, was die Lötstabilität der Bauteile beeinträchtigt. Für diese neuen Leiterplatten müssen die Testparameter für hohe und niedrige Temperaturen angepasst werden. Dies erfordert eine sanftere Temperaturanstiegs- und -abfallrate, eine höhere Anzahl von Zyklen und die Gewährleistung der Stabilität in extremen Temperaturumgebungen.

Hoch- und Tieftemperaturprüfungen dienen nicht nur der Qualitätssicherung, sondern bilden auch eine wichtige Grundlage für die Optimierung von Forschung und Entwicklung. Die Fehleranalyse ermöglicht die präzise Lokalisierung von Material- und Prozessfehlern und liefert wichtige Anhaltspunkte für die Verbesserung des Leiterplattendesigns.

Holen Sie sich den neuesten Preis? Wir werden so schnell wie möglich antworten (innerhalb von 12 Stunden)